Public Types |

Public Member Functions |

Protected Member Functions |

Protected Attributes |

List of all members

axi::pe::simple_target< BUSWIDTH, TYPES, N, POL > Class Template Reference

#include <simple_target.h>

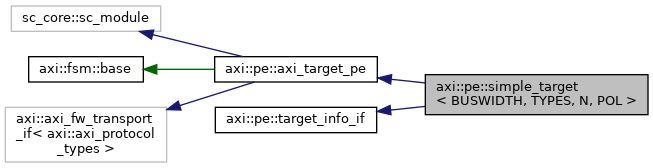

Inheritance diagram for axi::pe::simple_target< BUSWIDTH, TYPES, N, POL >:

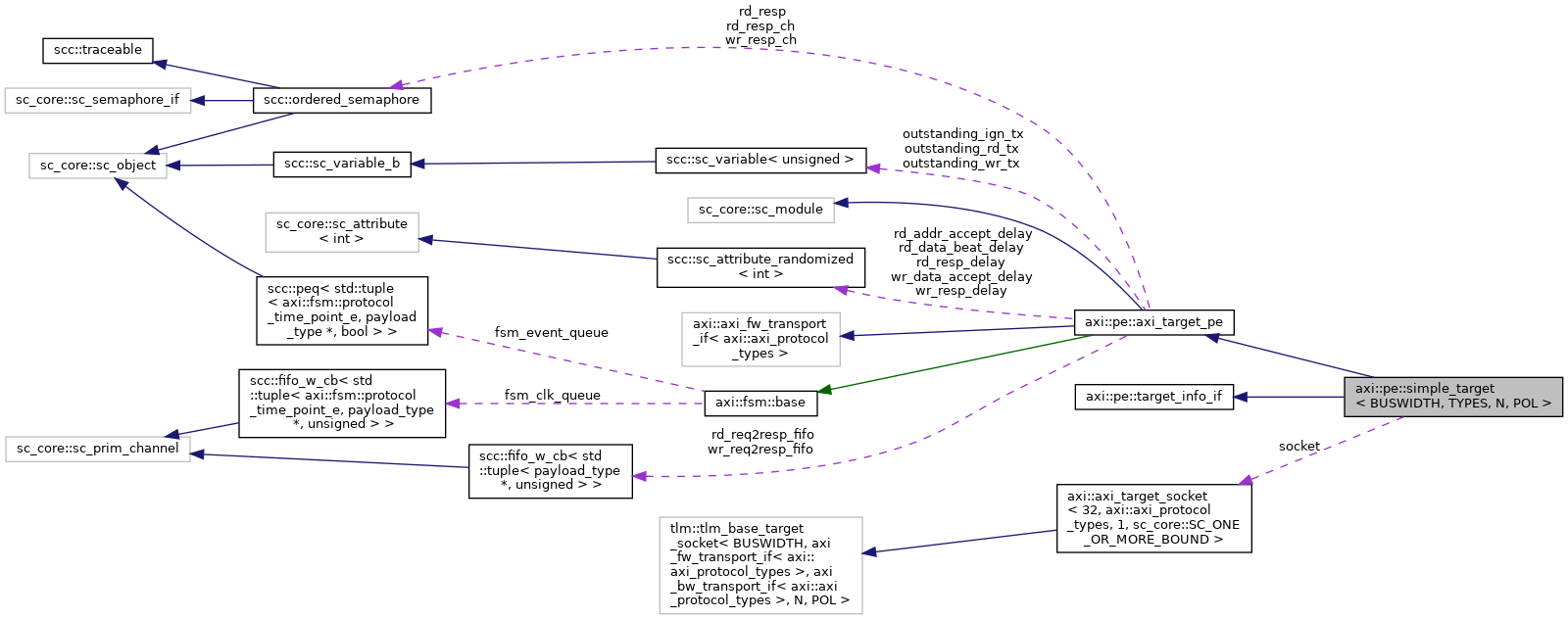

Collaboration diagram for axi::pe::simple_target< BUSWIDTH, TYPES, N, POL >:

Public Types | |

| using | base = axi_target_pe |

| using | payload_type = base::payload_type |

| using | phase_type = base::phase_type |

Public Types inherited from axi::pe::axi_target_pe Public Types inherited from axi::pe::axi_target_pe | |

| using | payload_type = axi::axi_protocol_types::tlm_payload_type |

| using | phase_type = axi::axi_protocol_types::tlm_phase_type |

Public Member Functions | |

| simple_target (axi::axi_target_socket< BUSWIDTH, TYPES, N, POL > &socket) | |

| the constructor More... | |

| simple_target (const sc_core::sc_module_name &nm, axi::axi_target_socket< BUSWIDTH, TYPES, N, POL > &socket, flavor_e flavor=flavor_e::AXI) | |

| simple_target (simple_target const &)=delete | |

| simple_target (simple_target &&)=delete | |

| simple_target & | operator= (simple_target const &)=delete |

| simple_target & | operator= (simple_target &&)=delete |

| size_t | get_outstanding_tx_count () override |

Public Member Functions inherited from axi::pe::axi_target_pe Public Member Functions inherited from axi::pe::axi_target_pe | |

| void | b_transport (payload_type &trans, sc_core::sc_time &t) override |

| tlm::tlm_sync_enum | nb_transport_fw (payload_type &trans, phase_type &phase, sc_core::sc_time &t) override |

| bool | get_direct_mem_ptr (payload_type &trans, tlm::tlm_dmi &dmi_data) override |

| unsigned int | transport_dbg (payload_type &trans) override |

| void | set_operation_cb (std::function< unsigned(payload_type &trans)> cb) |

| Set the operation callback function. More... | |

| void | operation_resp (payload_type &trans, unsigned clk_delay=0) |

| bool | is_active () |

| const sc_core::sc_event & | tx_finish_event () |

| axi_target_pe (const sc_core::sc_module_name &nm, size_t transfer_width, flavor_e flavor=flavor_e::AXI) | |

| void | set_bw_interface (axi::axi_bw_transport_if< axi_protocol_types > *ifs) |

| unsigned | getAllOutStandingTx () const |

Protected Member Functions | |

| void | end_of_elaboration () override |

Protected Member Functions inherited from axi::pe::axi_target_pe Protected Member Functions inherited from axi::pe::axi_target_pe | |

| axi_target_pe (axi_target_pe const &)=delete | |

| axi_target_pe (axi_target_pe &&)=delete | |

| axi_target_pe & | operator= (axi_target_pe const &)=delete |

| axi_target_pe & | operator= (axi_target_pe &&)=delete |

| void | end_of_elaboration () override |

| void | start_of_simulation () override |

| void | fsm_clk_method () |

| fsm::fsm_handle * | create_fsm_handle () override |

| void | setup_callbacks (fsm::fsm_handle *) override |

| unsigned | operations_callback (payload_type &trans) |

| void | process_req2resp_fifos () |

| void | start_rd_resp_thread () |

| void | start_wr_resp_thread () |

| void | send_wr_resp_beat_thread () |

| void | send_rd_resp_beat_thread () |

| scc::sc_variable< unsigned > & | getOutStandingTx (tlm::tlm_command cmd) |

| scc::sc_variable< unsigned > | getOutStandingTx (tlm::tlm_command cmd) const |

| void | nb_fw (payload_type &trans, const phase_type &phase) |

Protected Member Functions inherited from axi::fsm::base Protected Member Functions inherited from axi::fsm::base | |

| base (size_t transfer_width, bool coherent=false, axi::fsm::protocol_time_point_e wr_start=axi::fsm::RequestPhaseBeg) | |

| the constructor More... | |

| virtual | ~base () |

| the destructor | |

| tlm::tlm_sync_enum | nb_fw (payload_type &trans, phase_type const &phase, sc_core::sc_time &t) |

| triggers the FSM based on TLM phases in the forward path. Should be called from np_transport_fw of the respective derived class More... | |

| tlm::tlm_sync_enum | nb_bw (payload_type &trans, phase_type const &phase, sc_core::sc_time &t) |

| triggers the FSM based on TLM phases in the backward path. Should be called from np_transport_bw of the respective derived class More... | |

| axi::fsm::fsm_handle * | find_or_create (payload_type *gp=nullptr, bool ace=false) |

| retrieve the FSM handle based on the transaction passed. If non exist one will be created More... | |

| void | process_fsm_event () |

| processes the fsm_event_queue and triggers FSM aligned | |

| void | process_fsm_clk_queue () |

| processes the fsm_clk_queue and triggers the FSM accordingly. Should be registered as rising-edge clock callback | |

| void | schedule (axi::fsm::protocol_time_point_e e, tlm::scc::tlm_gp_shared_ptr &gp, unsigned cycles) |

| processes the fsm_sched_queue and propagates events to fsm_clk_queue. Should be registered as falling-edge clock callback | |

| void | schedule (axi::fsm::protocol_time_point_e e, payload_type *gp, unsigned cycles) |

| void | schedule (axi::fsm::protocol_time_point_e e, tlm::scc::tlm_gp_shared_ptr &gp, sc_core::sc_time delay, bool syncronize=false) |

| processes the fsm_sched_queue and propagates events to fsm_clk_queue. Should be registered as falling-edge clock callback | |

| void | schedule (axi::fsm::protocol_time_point_e e, payload_type *gp, sc_core::sc_time delay, bool syncronize=false) |

| void | react (axi::fsm::protocol_time_point_e event, tlm::scc::tlm_gp_shared_ptr &trans) |

| triggers the FSM with event and given transaction More... | |

| void | react (axi::fsm::protocol_time_point_e event, payload_type *trans) |

| void | react (axi::fsm::protocol_time_point_e, axi::fsm::fsm_handle *) |

Protected Attributes | |

| axi::axi_target_socket< BUSWIDTH, TYPES, N, POL > & | socket |

Protected Attributes inherited from axi::pe::axi_target_pe Protected Attributes inherited from axi::pe::axi_target_pe | |

| axi::axi_bw_transport_if< axi_protocol_types > * | socket_bw {nullptr} |

| std::function< unsigned(payload_type &trans)> | operation_cb |

| scc::fifo_w_cb< std::tuple< payload_type *, unsigned > > | rd_req2resp_fifo {"rd_req2resp_fifo"} |

| scc::fifo_w_cb< std::tuple< payload_type *, unsigned > > | wr_req2resp_fifo {"wr_req2resp_fifo"} |

| sc_core::sc_fifo< payload_type * > | rd_resp_fifo {1} |

| sc_core::sc_fifo< payload_type * > | wr_resp_fifo {1} |

| sc_core::sc_fifo< std::tuple< fsm::fsm_handle *, axi::fsm::protocol_time_point_e > > | wr_resp_beat_fifo {128} |

| sc_core::sc_fifo< std::tuple< fsm::fsm_handle *, axi::fsm::protocol_time_point_e > > | rd_resp_beat_fifo {128} |

| scc::ordered_semaphore | rd_resp {1} |

| scc::ordered_semaphore | wr_resp_ch {1} |

| scc::ordered_semaphore | rd_resp_ch {1} |

| sc_core::sc_clock * | clk_if {nullptr} |

| std::unique_ptr< bw_intor_impl > | bw_intor |

| std::array< unsigned, 3 > | outstanding_cnt {{0, 0, 0}} |

| scc::sc_variable< unsigned > | outstanding_rd_tx {"OutstandingRd", 0} |

| scc::sc_variable< unsigned > | outstanding_wr_tx {"OutstandingWr", 0} |

| scc::sc_variable< unsigned > | outstanding_ign_tx {"OutstandingIgn", 0} |

| std::array< tlm::tlm_generic_payload *, 3 > | stalled_tx {nullptr, nullptr, nullptr} |

| std::array< axi::fsm::protocol_time_point_e, 3 > | stalled_tp {{axi::fsm::CB_CNT, axi::fsm::CB_CNT, axi::fsm::CB_CNT}} |

| tlm_utils::peq_with_cb_and_phase< axi_target_pe > | fw_peq {this, &axi_target_pe::nb_fw} |

| std::unordered_set< unsigned > | active_rdresp_id |

Protected Attributes inherited from axi::fsm::base Protected Attributes inherited from axi::fsm::base | |

| ::scc::peq< std::tuple< axi::fsm::protocol_time_point_e, payload_type *, bool > > | fsm_event_queue |

| ::scc::fifo_w_cb< std::tuple< axi::fsm::protocol_time_point_e, payload_type *, unsigned > > | fsm_clk_queue |

| sc_core::sc_process_handle | fsm_clk_queue_hndl |

| size_t | transfer_width_in_bytes |

| const axi::fsm::protocol_time_point_e | wr_start |

| const bool | coherent |

| std::unordered_map< payload_type *, axi::fsm::fsm_handle * > | active_fsm |

| std::deque< axi::fsm::fsm_handle * > | idle_fsm |

| std::vector< std::unique_ptr< axi::fsm::fsm_handle > > | allocated_fsm |

| std::string | instance_name |

| sc_core::sc_event | finish_evt |

Additional Inherited Members | |

Public Attributes inherited from axi::pe::axi_target_pe Public Attributes inherited from axi::pe::axi_target_pe | |

| sc_core::sc_in< bool > | clk_i {"clk_i"} |

| sc_core::sc_port< tlm::scc::pe::intor_fw_nb, 1, sc_core::SC_ZERO_OR_MORE_BOUND > | fw_o {"fw_o"} |

| sc_core::sc_export< tlm::scc::pe::intor_bw_nb > | bw_i {"bw_i"} |

| cci::cci_param< unsigned > | max_outstanding_tx {"max_outstanding_tx", 0} |

| the number of supported outstanding transactions. If this limit is reached the target starts to do back-pressure | |

| cci::cci_param< bool > | rd_data_interleaving {"rd_data_interleaving", true} |

| enable data interleaving on read responses if rd_data_beat_delay is greater than 0 | |

| cci::cci_param< int > | wr_data_accept_delay {"wr_data_accept_delay", 0} |

| the latency between between BEGIN(_PARTIAL)_REQ and END(_PARTIAL)_REQ (AWVALID to AWREADY and WVALID to WREADY) -> AWR, WBR | |

| cci::cci_param< int > | rd_addr_accept_delay {"rd_addr_accept_delay", 0} |

| the latency between between BEGIN_REQ and END_REQ (ARVALID to ARREADY) -> APR | |

| cci::cci_param< int > | rd_data_beat_delay {"rd_data_beat_delay", 0} |

| the latency between between END(_PARTIAL)_RESP and BEGIN(_PARTIAL)_RESP (RREADY to RVALID) -> RBV | |

| cci::cci_param< int > | rd_resp_delay {"rd_resp_delay", 0} |

| the latency between request and response phase. Will be overwritten by the return of the callback function (if registered) -> RIV | |

| cci::cci_param< int > | wr_resp_delay {"wr_resp_delay", 0} |

| the latency between request and response phase. Will be overwritten by the return of the callback function (if registered) -> BV | |

Protected Types inherited from axi::fsm::base Protected Types inherited from axi::fsm::base | |

| using | payload_type = axi::axi_protocol_types::tlm_payload_type |

| aliases used in the class | |

| using | phase_type = axi::axi_protocol_types::tlm_phase_type |

Detailed Description

template<unsigned int BUSWIDTH = 32, typename TYPES = axi::axi_protocol_types, int N = 1, sc_core::sc_port_policy POL = sc_core::SC_ONE_OR_MORE_BOUND>

class axi::pe::simple_target< BUSWIDTH, TYPES, N, POL >

the target socket protocol engine(s) adapted to a particular target socket configuration

- Deprecated:

- Use ordered_/reordering_target instead

Definition at line 33 of file simple_target.h.

Constructor & Destructor Documentation

◆ simple_target()

template<unsigned int BUSWIDTH = 32, typename TYPES = axi::axi_protocol_types, int N = 1, sc_core::sc_port_policy POL = sc_core::SC_ONE_OR_MORE_BOUND>

|

inline |

the constructor

- Parameters

-

socket reference to the initiator socket used to send and receive transactions

Definition at line 43 of file simple_target.h.

The documentation for this class was generated from the following file:

- /home/eyck/git/SystemC-Components/third_party/axi_chi/axi/pe/simple_target.h