|

| | memory (const sc_core::sc_module_name &nm) |

| void | set_operation_callback (std::function< int(memory< SIZE, BUSWIDTH > &, tlm::tlm_generic_payload &, sc_core::sc_time &delay)> cb) |

| | allows to register a callback or functor being invoked upon an access to the memory

|

| void | set_dmi_callback (std::function< bool(memory< SIZE, BUSWIDTH > &, tlm::tlm_generic_payload &, tlm::tlm_dmi &)> cb) |

| | allows to register a callback or functor being invoked upon a direct memory access (DMI) to the memory

|

| void | map_host_memory (uint64_t base, uint64_t size, uint8_t *ptr) |

| | maps a given memory into the address range of the TLM memory

|

| void | unmap_host_memory (uint64_t base, uint64_t size) |

| | unmpas a host memory mapped into the address range of the TLM memory

|

| int | handle_operation (tlm::tlm_generic_payload &trans, sc_core::sc_time &delay) |

| | ! handle the memory operation independent on interface function used

|

| bool | handle_dmi (tlm::tlm_generic_payload &gp, tlm::tlm_dmi &dmi_data) |

| | handle the dmi functionality

|

|

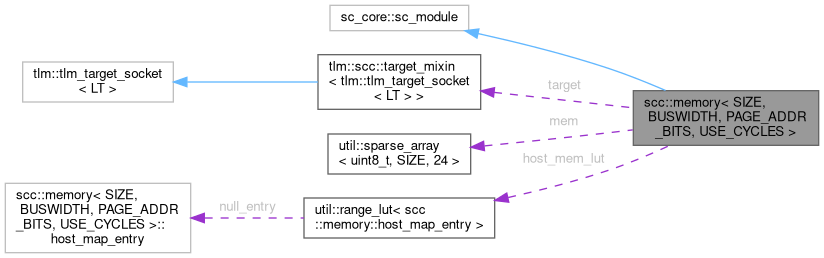

| tlm::scc::target_mixin< tlm::tlm_target_socket< BUSWIDTH > > | target {"ts"} |

| | the target socket to connect to TLM

|

| cci::cci_param< bool > | allow_dmi {"allow_dmi", true, "Allow DMI accesses to this memory if set"} |

| | allow DMI accesses

|

| cci::cci_param< delay_type > | rd_resp_delay {"rd_resp_delay", delay_spec_type<USE_CYCLES>::get_default_val()} |

| | read response delay in cycles if USE_CYCLES==true else in sc_core::sc_time

|

| cci::cci_param< delay_type > | wr_resp_delay {"wr_resp_delay", delay_spec_type<USE_CYCLES>::get_default_val()} |

| | write response delay in cycles if USE_CYCLES==true else in sc_core::sc_time

|

| std::function< int(memory< SIZE, BUSWIDTH > &, tlm::tlm_generic_payload &, sc_core::sc_time &delay)> | operation_cb |

| std::function< bool(memory< SIZE, BUSWIDTH > &, tlm::tlm_generic_payload &, tlm::tlm_dmi &)> | dmi_cb |

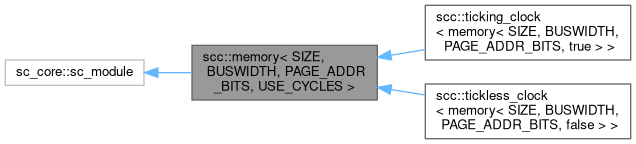

template<unsigned long long SIZE, unsigned BUSWIDTH = LT, unsigned PAGE_ADDR_BITS = 24, bool USE_CYCLES = false>

class scc::memory< SIZE, BUSWIDTH, PAGE_ADDR_BITS, USE_CYCLES >

simple TLM2.0 LT memory model

This model uses the util::sparse_array as backing store. Therefore it can have an arbitrary size since only pages for accessed addresses are allocated. it is possible to map specific host memory ranges to a target memory range. For this the scc::host_mem_map_extension hs to be used in conjunction with the TLM_IGNORE_COMMAND. The extension carries the pointer to the host memory to be used while the generic payload address and length indicate the size of the memory block

TODO: add some more parameters to configure allowed access types (rw, read only)

- Template Parameters

-

| SIZE | size of the memery |

| BUSWIDTH | bus width of the socket |

Definition at line 70 of file memory.h.

template<unsigned long long SIZE, unsigned BUSWIDTH, unsigned PAGE_ADDR_BITS, bool USE_CYCLES>

| scc::memory< SIZE, BUSWIDTH, PAGE_ADDR_BITS, USE_CYCLES >::memory |

( |

const sc_core::sc_module_name & | nm | ) |

|

constructor with explicit instance name

- Parameters

-

implementation details ///////////////////////////////////////////////////////////////////////////

Definition at line 197 of file memory.h.

template<unsigned long long SIZE, unsigned BUSWIDTH = LT, unsigned PAGE_ADDR_BITS = 24, bool USE_CYCLES = false>

| void scc::memory< SIZE, BUSWIDTH, PAGE_ADDR_BITS, USE_CYCLES >::map_host_memory |

( |

uint64_t | base, |

|

|

uint64_t | size, |

|

|

uint8_t * | ptr ) |

|

inline |

maps a given memory into the address range of the TLM memory

- Parameters

-

| base | base address where the memory shall be mapped |

| size | size of the memory range to map |

| ptr | pointer to the mapped host memory |

Definition at line 131 of file memory.h.

template<unsigned long long SIZE, unsigned BUSWIDTH = LT, unsigned PAGE_ADDR_BITS = 24, bool USE_CYCLES = false>

| void scc::memory< SIZE, BUSWIDTH, PAGE_ADDR_BITS, USE_CYCLES >::set_dmi_callback |

( |

std::function< bool(memory< SIZE, BUSWIDTH > &, tlm::tlm_generic_payload &, tlm::tlm_dmi &)> | cb | ) |

|

|

inline |

allows to register a callback or functor being invoked upon a direct memory access (DMI) to the memory

- Parameters

-

| cb | the callback function or functor |

Definition at line 109 of file memory.h.

template<unsigned long long SIZE, unsigned BUSWIDTH = LT, unsigned PAGE_ADDR_BITS = 24, bool USE_CYCLES = false>

| void scc::memory< SIZE, BUSWIDTH, PAGE_ADDR_BITS, USE_CYCLES >::set_operation_callback |

( |

std::function< int(memory< SIZE, BUSWIDTH > &, tlm::tlm_generic_payload &, sc_core::sc_time &delay)> | cb | ) |

|

|

inline |

allows to register a callback or functor being invoked upon an access to the memory

- Parameters

-

| cb | the callback function or functor |

Definition at line 100 of file memory.h.

template<unsigned long long SIZE, unsigned BUSWIDTH = LT, unsigned PAGE_ADDR_BITS = 24, bool USE_CYCLES = false>

| void scc::memory< SIZE, BUSWIDTH, PAGE_ADDR_BITS, USE_CYCLES >::unmap_host_memory |

( |

uint64_t | base, |

|

|

uint64_t | size ) |

|

inline |

unmpas a host memory mapped into the address range of the TLM memory

- Parameters

-

| base | base address where the memory shall be mapped |

| size | size of the memory range to map |

Definition at line 145 of file memory.h.