|

| sc_core::sc_in< bool > | clk_i {"clk_i"} |

| sc_core::sc_export< tlm::scc::pe::intor_fw_nb > | fw_i {"fw_i"} |

| sc_core::sc_port< tlm::scc::pe::intor_bw_nb, 1, sc_core::SC_ZERO_OR_MORE_BOUND > | bw_o {"bw_o"} |

| cci::cci_param< int > & | rd_resp_delay |

| | the latency between request and response phase. Will be overwritten by the return of the callback function (if registered) -> RIV

|

| cci::cci_param< int > & | wr_resp_delay |

| | the latency between request and response phase. Will be overwritten by the return of the callback function (if registered) -> BV

|

| cci::cci_param< double > | rd_bw_limit_byte_per_sec {"rd_bw_limit_byte_per_sec", -1.0} |

| | the bandwidth limit for read accesses. A value of -1 disables the limiting

|

| cci::cci_param< double > | wr_bw_limit_byte_per_sec {"wr_bw_limit_byte_per_sec", -1.0} |

| | the bandwidth limit for write accesses. A value of -1 disables the limiting

|

| cci::cci_param< double > | total_bw_limit_byte_per_sec {"total_bw_limit_byte_per_sec", -1.0} |

| | the bandwidth limit for read accesses. A value of -1 disables the limiting

|

Definition at line 27 of file ordered_target.h.

◆ rate_limiting_buffer()

| axi::pe::rate_limiting_buffer::rate_limiting_buffer |

( |

const sc_core::sc_module_name & | nm, |

|

|

cci::cci_param< int > & | rd_resp_delay, |

|

|

cci::cci_param< int > & | wr_resp_delay ) |

◆ end_of_elaboration()

| void axi::pe::rate_limiting_buffer::end_of_elaboration |

( |

| ) |

|

|

overrideprotected |

◆ process_req2resp_fifos()

| void axi::pe::rate_limiting_buffer::process_req2resp_fifos |

( |

| ) |

|

|

protected |

◆ snoop_resp()

| void axi::pe::rate_limiting_buffer::snoop_resp |

( |

tlm::tlm_generic_payload & | payload, |

|

|

bool | sync = false ) |

|

inlineoverridevirtual |

send a response to a backward transaction if not immediately answered

- Parameters

-

| payload | object with (optional) extensions |

| sync | if true send with next rising clock edge of the pe otherwise send it immediately |

Implements tlm::scc::pe::intor_fw< type::NB >.

Definition at line 74 of file ordered_target.h.

◆ start_of_simulation()

| void axi::pe::rate_limiting_buffer::start_of_simulation |

( |

| ) |

|

|

overrideprotected |

◆ start_rd_resp_thread()

| void axi::pe::rate_limiting_buffer::start_rd_resp_thread |

( |

| ) |

|

|

protected |

◆ start_wr_resp_thread()

| void axi::pe::rate_limiting_buffer::start_wr_resp_thread |

( |

| ) |

|

|

protected |

◆ transport()

| void axi::pe::rate_limiting_buffer::transport |

( |

tlm::tlm_generic_payload & | payload, |

|

|

bool | lt_transport = false ) |

|

overridevirtual |

execute the transport of the payload. Independent of the underlying layer this function is blocking

- Parameters

-

| payload | object with (optional) extensions |

| lt_transport | use b_transport instead of nb_transport* |

Implements tlm::scc::pe::intor_fw< type::NB >.

Definition at line 42 of file ordered_target.cpp.

◆ bw_o

◆ clk_i

| sc_core::sc_in<bool> axi::pe::rate_limiting_buffer::clk_i {"clk_i"} |

◆ clk_if

| sc_core::sc_clock* axi::pe::rate_limiting_buffer::clk_if {nullptr} |

|

protected |

◆ fw_i

◆ rd_bw_limit_byte_per_sec

| cci::cci_param<double> axi::pe::rate_limiting_buffer::rd_bw_limit_byte_per_sec {"rd_bw_limit_byte_per_sec", -1.0} |

the bandwidth limit for read accesses. A value of -1 disables the limiting

Definition at line 48 of file ordered_target.h.

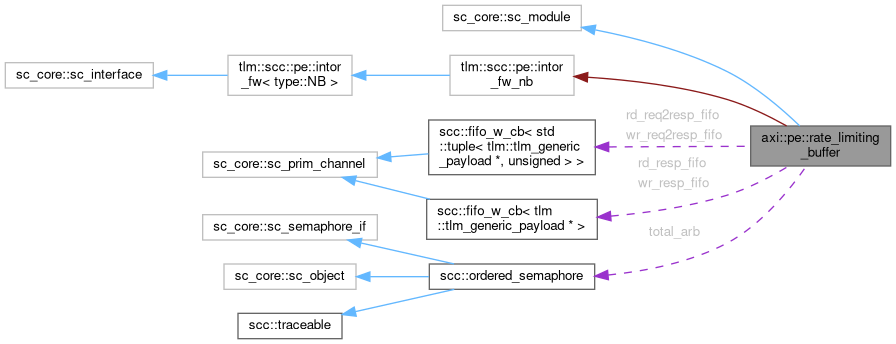

◆ rd_req2resp_fifo

| scc::fifo_w_cb<std::tuple<tlm::tlm_generic_payload*, unsigned> > axi::pe::rate_limiting_buffer::rd_req2resp_fifo {"rd_req2resp_fifo"} |

|

protected |

◆ rd_resp_delay

| cci::cci_param<int>& axi::pe::rate_limiting_buffer::rd_resp_delay |

the latency between request and response phase. Will be overwritten by the return of the callback function (if registered) -> RIV

Definition at line 39 of file ordered_target.h.

◆ rd_resp_fifo

| scc::fifo_w_cb<tlm::tlm_generic_payload*> axi::pe::rate_limiting_buffer::rd_resp_fifo {"rd_resp_fifo"} |

|

protected |

◆ time_per_byte_rd

| sc_core::sc_time axi::pe::rate_limiting_buffer::time_per_byte_rd |

|

protected |

◆ time_per_byte_total

| sc_core::sc_time axi::pe::rate_limiting_buffer::time_per_byte_total |

|

protected |

◆ time_per_byte_wr

| sc_core::sc_time axi::pe::rate_limiting_buffer::time_per_byte_wr |

|

protected |

◆ total_arb

◆ total_bw_limit_byte_per_sec

| cci::cci_param<double> axi::pe::rate_limiting_buffer::total_bw_limit_byte_per_sec {"total_bw_limit_byte_per_sec", -1.0} |

the bandwidth limit for read accesses. A value of -1 disables the limiting

Definition at line 56 of file ordered_target.h.

◆ total_residual_clocks

| double axi::pe::rate_limiting_buffer::total_residual_clocks {0.0} |

|

protected |

◆ wr_bw_limit_byte_per_sec

| cci::cci_param<double> axi::pe::rate_limiting_buffer::wr_bw_limit_byte_per_sec {"wr_bw_limit_byte_per_sec", -1.0} |

the bandwidth limit for write accesses. A value of -1 disables the limiting

Definition at line 52 of file ordered_target.h.

◆ wr_req2resp_fifo

| scc::fifo_w_cb<std::tuple<tlm::tlm_generic_payload*, unsigned> > axi::pe::rate_limiting_buffer::wr_req2resp_fifo {"wr_req2resp_fifo"} |

|

protected |

◆ wr_resp_delay

| cci::cci_param<int>& axi::pe::rate_limiting_buffer::wr_resp_delay |

the latency between request and response phase. Will be overwritten by the return of the callback function (if registered) -> BV

Definition at line 44 of file ordered_target.h.

◆ wr_resp_fifo

| scc::fifo_w_cb<tlm::tlm_generic_payload*> axi::pe::rate_limiting_buffer::wr_resp_fifo {"wr_resp_fifo"} |

|

protected |

The documentation for this class was generated from the following files:

- /home/eyck/Projects/MINRES/SystemC-Components/third_party/axi_chi/axi/pe/ordered_target.h

- /home/eyck/Projects/MINRES/SystemC-Components/third_party/axi_chi/axi/pe/ordered_target.cpp